ISSN 2959-6157

# Analysis of The Recent Volatile Memory Cells-DRAM and SRAM

## Zimo Zhang<sup>1,\*</sup>

<sup>1</sup>Zhengzhou Middle school, Zhengzhou, China

\*Corresponding author: zhangzimo@outlook.com

#### Abstract:

Memory cells are basic composition units in advanced electronic equipment like computers. According to the rapid development in memory cells market and data storing industry, the intelligent new technology would absorb plenty of benefits in memory cells. The memory cells industry could be separated into two prime facets, the volatile memory cells and non-volatile memory cells. Both of them are trying to adapt the main requirement and demand of current market, while the volatile and nonvolatile memory cells are pursuing more flexible and fantastic functions. This academic article only discusses of the volatile memory cells including Dynamic Random Access Memory (DRAM), Static Random Access Memory (SRAM). Therefore, the concepts and fundamental information of volatile memory cells would be shown first. In addition, the essay focuses on mentioning the well-known applications of volatile memory cells. A brief analysis on the situations and optimizations of volatile memory cells would be revealed in the last part of essay before the final conclusion.

**Keywords:** Volatile memory cells, Dynamic Random Access Memory, Static Random Access Memory

### **1. Introduction**

The images and curiosity of human prompt the development of computer hardware technology, and one of them is the storing technology by memory cells [1]. The memory cells technology has become well-known many decades ago and start to dominate the relative market. They have different kinds and play a crucial role in chips industry and new electronic devices with smaller volume. Until now, the memory cells technology has expanded to a vast and mature industry that contains a wealth of sorts of memory cells. The total of memory cells could be divides into two main part, the volatile memory cells and non-volatile memory cells. Further, Dynamic Random Access memory cells (DRAM) and Static Random Access Memory (SRAM) are the most vital components of volatile memory.

Therefore, this essay will mainly focus on the development process and structures in the first step. Then, the applications like wireless devices would be analyzed in the next stage which includes three popular applications recently. Finally, this essay discusses about the current situations of two volatile memory ISSN 2959-6157

cells (DRAM and SRAM), and also outlines some of potential optimizations of both DRAM and SRAM. A conclusion will be shown at the end of the article.

### 2. The fundamental theories and structures of volatile memory cells

The volatile memory cells are one of the most popular and fundamental memory cells in the electronic technology. It consists of two basic memory cells Dynamic Random Access Memory and Static Random Access Memory. Both of them play a crucial role in modern technologies and industries, such as data computing, emerging AI devices, wireless sensor devices and IoT devices. From the basic theories of volatile memory cells, it is a kind of memory hardware that could store the data in a really high speed. Hence, the storing in here is efficient and economical. One of the demerits of volatile memory cells is the data storing in volatile memory cells is temporary and momentary, which is means that the numbers in memory cells will disappear when the power is lost. It will strongly affect the efficiency and safety of the data storing. This problem could not be neglected in any sorts of volatile memory cells. That is why the non-volatile memory cells started to be widely used in high technology. DRAM and SRAM is the most famous and familiar volatile memory cells, which have been extensively used for several decades in global world. They have distinct functions and structures in storing.

#### 2.1 Dynamic Random Access Memory (DRAM)

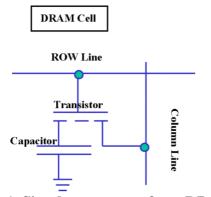

DRAM is the most traditional and common memory cell in this industry. The basic structure of DRAM is shown in figure 1.

#### Figure 1. Simple structure of one DRAM memory cells in whole DRAM reading system [2]

This figure 1 apparently illustrate that the basic units and components in a single DRAM memory cell, which con-

tains a transistor, a capacitor row line and the Column line. The capacitor is connected with ground. More common names of row line and column line is word line and bit line respectively. The reading procedure could be done in a rapid and extremely simple way in DRAM. When the transistor allows the current to pass through, the capacitor will be charged in a high speed because the capacitor have different structure from normal current source. The total process only takes few nanoseconds. When the transistor is closed, the current stops the flow through the transistor and the capacitor will be still fully charged. If there is no voltage that could force the electric charges onto the capacitor, when the transistor creates an entrance to the lines, the electric charges will flow to the outside of DRAM until the charges disappear. It is the main theory of how a DRAM unit operates in computer circuit and other electronic devices. On the other hand, this structure would also relate to the representing and reading of data. The inventors use the binary system to symbolize the data. To be more specific, the capacitor represented the number '1' in the binary system when it is fully charged by electric charges. In comparison, it represents the number '0' when the capacitor lost the electric charges. Some of the contemporary electronic devices utilize the whole DRAM array to cope with the storing work in normal situation. However, the reading procedure would be seen as a more complicated one. In the DRAM array, millions of DRAM units will be connected with thousands of word lines and bit lines. Then, there are a few sense amplifiers settled in the end of bit lines. Hence, it is not possible that reading a particular data in the DRAM system. Attributing the success to the simple and ingenious structure, both of the storing and reading procedures are efficient. In addition, the cost of storing is also low in DRAM. Therefore, the DRAM became the significantly prevalent a few decades ago. However, the DRAM has a vital drawback which could strongly influence or even block the development prospect of DRAM: 'Destructive Reading'. It indicates that the data need to be write again after you read once. So, the data would reenter instantly in the DRAM reading mode. The mainstream point of view in memory cells field is that the function and utilization of dynamic random-access memory are facing the risks and limitations, which is mean the DRAM technology is coming to a destination [1]. But there is no doubt that the DRAM has already developed a lot in nearly 50 years, such as the 6 times enhancement in capacity and density of DRAM [3].

#### 2.2 Static Random Access Memory (SRAM)

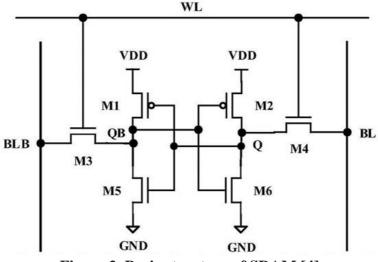

SRAM is the most familiar and popular memory cells in modern technologies like chips. Comparing with the

DRAM, many improvements have been made in the basic theory and structure of SRAM. Specifically, the SRAM structure contains 6 transistors, whereas the DRAM only has one. 6 transistors could ensure the stability of memory cells. The fundamental structure of SRAM is shown in figure 2.

Figure 2. Basic structure of SRAM [4]

The picture thorough shows the operation principles of the Static Random Access Memory. It is evident that one unit of SRAM connects with one word line and twobit lines, in order to read to data in a steady way. In the memory research field, the structure of SRAM is seen as the most classical and practical one which is mentioned in Shuai Chen's paper [5]. The design of 6 transistors creates a 'bistable structure' that could enhance the function of SRAM rapidly. The most substantial development in SRAM is getting rid of the 'Destructive Reading'. SRAM use 6 transistors to create a new model which could store and express data in a more reasonable way. The connected point between M1 and M5 is QB, and the connected point on another side is called Q. Both of them are created for measuring the high-level voltage or low-level voltage in SRAM. If the point QB has a high-level voltage, it represents the number '1'in binary system. In contrast, the Q has a higher-level voltage, it will represent '0' in binary system. Then, the bit lines in SRAM take the responsibility of data reading. Then number'0'would be read in the left bit line while the number'1'would be read on the another side if the right side has a larger level of voltage. Except the remove of 'destructive reading', SRAM has enormous merits comparing to DRAM. From the most crucial aspect, Static Random Access Memory has an extreme high operational speed. Despite this, its complex structure allows it to deal with the puzzles that DRAM cannot. However, the complex structure directly led to more cost and more large-scale volume, which means that the integration density would become lower. Overall, the fundamental theory of SRAM is meaningful and innovative, this kind of classical SRAM structure is still being used in global memory cells market.

# **3.** The application of volatile memory cells

Since the invention of DRAM in considerable number of years before, the memory cells started to become famous in electrical devices industry and global market. In recent years, many of the application of DRAM and SRAM are associated with high technologies fields.

#### 3.1 In low voltage devices

The electronic devices with very low voltage are occupying individuals' lives rapidly, such as wearable devices, wireless sensor devices and IoT devices (Internet of things). The low voltage technology requires the low cost memory cells and also with high density, which could be putted in chips in an enormous number as mentioned in Writam Banerjee's paper [6]. As for the modes of DRAM and SRAM, they have much more obvious advantages on the cost-efficiency and density than the other kinds of memory cells like Flash memory. Hence, they can obtain a high position in low voltage devices in the market because they have the ability of being placed in chips or monitors with very low cost. Masood Qazi claims that although the SRAM master the capability of working in low voltage products, it will partly have a detrimental impact on the area and function in SRAM [7]. Therefore, it will cause some negative effects on SRAM to some extent. The DRAM has been used in low voltage devices for a long

ISSN 2959-6157

period. The common low voltage electrical devices require the high density of memory cells in chips, which means the total number of memory cells. Comparing to the frame of SRAM, the structure of DRAM with single transistor has higher cost performance to fill the chips with abundant number of DRAM cells in an affordable expense. Not only about cost performance that the DRAM memory cells have lesser volume than the other memory cells. It is the most concise and elementary cells in memory technologies. Hence, the DRAM memory cells have the largest number that could be putted in power or voltage restricted devices. In some other ways, the optimization of DRAM could also associate with emerging technology like the SOI technology with SOC process. Just like the example contended by experts that the production of 16-Mbit SOI DRAM with 0.3- m has gained the great achievement in SOC structure [8].

#### 3.2 In artificial intelligence

Artificial intelligence is the one of the most popular research aspects that requiring a mass of high techniques, advanced facilities and participation of researchers. The application of DRAM memory cells has reached a high level. It is evident that the AI faced the difficulties of data processing and the servers which is capable to AI technology [9]. Thus, the DRAM plays a vital role in coping with data and numbers in artificial intelligence, which accelerate the development of AI for several years. However, the DRAM application is being influenced by many of factors. The most important one is the challenge on scaling complexity and cost. Until now, DRAM is not be recognized as a major side of data processing in artificial intelligence. The manufacturers of DRAM also offer less DRAM than before. What sets it apart from other applications is the situation of SRAM.SRAM also struggled with the manufacturing cost and scaling part [9]. The development of artificial intelligence is more focusing on the cost and density, rather than sophisticated framework and excellent functions like the SRAM with 6 transistors. Therefore, the scientists in AI research program are chasing for other reasonable substitutions. In fact, the emerging memory cells with low cost might be the prior choice of new substitution. The MRAM is one of the possible alternates which not only has power advantages but also cost-effective than old volatile memory cells [9]. The DRAM and SRAM are out of mainstream in AI.

#### 3.3 In Nanoscale field

The nanoscale field includes memory cells with smaller volume and higher accuracy. It is obvious that the DRAM has much easier access to minimize than SRAM. Actually, an increasing number of progressive nano devices are equipped with DRAM cells. The structure of DRAM decided that it has a easier to store data and also easier to be created as an array. Thus, the primary duty of DRAM in nanoscale devices is off-state leakage current which is mentioned by researchers [10]. That is the reason of why the scholars and scientists focusing more on reducing power release and enhancing the effectiveness rather than structure or other possible factors. In contrast, the SRAM has the ability of staying in high operational speed and being effective in circuit. Hence, it is widely used in some nanoscale equipment that people are familiar with like microprocessors and components in modern computers.

# 4. The challenges and optimization of volatile memory cells

#### 4.1 The situations and optimization of Dynamic Random Access Memory

Just like the other kind of memory cells, the main development aspect of DRAM is to reduce the volume of components in the DRAM system in order to reach the high quality in production and also diminish the cost it. The researchers claims that it is essential for manufacturers to more focus on the low cost and high yield of DRAM. To be more specific, they should more concentrate on the DRAM storage capacitor and low-leakage devices [11]. Among all the directions, the quality and operation life should be seen as the most momentous aspect. The DRAM technology has promoted a wealth of industries like AEROSPACE, medical equipment and even artificial intelligence. Therefore, the reliability is the most important factor that should be considered [12]. An increasing number of consortium and companies are striving on reducing the volume of transistor in order to make a more integrated DRAM system. However, the development speed of reducing the volume of transistor is far inferior from the development speed of emerging application industries. Hence, the project of dramatically enhancing the function of DRAM was out of the mainstream in volatile memory cells a few years ago. Nowadays, few of the related enterprises and factories do not put too much fund and employees in promoting the DRAM memory. Some experts even contend that the Dynamic Random-Access memory will be replaced by other memory cells with high reliability and faculties after a period.

# 4.2 The situations and optimization of Static Random Access Memory

The situations of Static Random Access Memory are

much more promising and optimistic than the DRAM one. It occupies abundant attentions and research funds in volatile memory cells exploring. In 2024, a crucial breakthrough could be found in SRAM circuit is that the requirement of voltage has already dropped to 500mV or even lower in SRAM with 6 transistors. In addition, the rank of production has been advanced to 14nm craft in SRAM system [1]. However, the technology level cannot afford the craft of SRAM to be more sophisticated, like to be smaller than 14nm. The utility and function will not have any great advance if the production craft of SRAM is lower than 14nm. Hence, the main point is to increase the density SRAM in integrated circuit and chips, rather than focusing on more precise craft [1]. The process of enhancing density of SRAM is also tough and laborious, which will not be easier as specifying the SRAM craft. So, the optimization procedure of SRAM is also encountering great puzzles like the DRAM. However, because of the brilliant structure and superb performance in electronic devices, the demand of SRAM will not be affected a lot in the future. It is concrete that equipment with SRAM memory cells will still be popular and irreplaceable in the coming period.

# **5.** Conclusion

Although the structures of both DRAM and SRAM have the capacity in coping with different aspects of applications, the potential functions and future applications are also being limited. The DRAM structure is restricted by the destructive reading. In contrast, DRAM is familiar with the high capacity and density in circuit while the SRAM has the most sophisticated structure in volatile memory cells. The demerit of destructive reading has been solved completely in SRAM with 6 transistors, whereas the cost of SRAM manufacturing is great high, and the volume of it is also larger than the other kinds of memory cells. The old styles of DRAM and SRAM need to be redesigned and produced to accomplish the more complex goal in recent years. Basically, both of DRAM and SRAM should pay attention to reduce the volume of transistors and capacitors in order to create a more space-consuming and complicated system in electronic tools. In fact, there is no fantastic solutions to completely replaces the functions of volatile memory cells, but is does not mean that the transformations of both of them are negligible. In the future, the applications of DRAM and SRAM would also popular in high techniques and gain a huge percentage of memory cells market if they try to transform and develop to a new dominant electronic component.

## 6. References

[1] Ning X, Guanghui F. Characteristics and Development Analysis of Semiconductor Storage Chips. Electronic technology, 2024, 53(04): 22-24.

[2] Lee M J, Jin S, Baek C K, et al. A proposal on an optimized device structure with experimental studies on recent devices for the DRAM cell transistor. IEEE Transactions on Electron Devices, 2007, 54(12): 3325-3335.

[3] Koyanagi M. History of MOS Memory Evolution on DRAM and SRAM. 75th Anniversary of the Transistor, 2023: 187-213.

[4] Razavipour G, Afzali-Kusha A, Pedram M. Design and analysis of two low-power SRAM cell structures. IEEE transactions on very large scale integration (VLSI) systems, 2009, 17(10): 1551-1555.

[5] Shuai C, Min C, Jifeng Z. A review of research on endogenous memory PUF in embedded systems. Integrated circuits and embedded systems, 2024.

[6] Banerjee W. Challenges and applications of emerging nonvolatile memory devices. Electronics, 2020, 9(6): 1029.

[7] Qazi M, Sinangil M, Chandrakasan A. Challenges and directions for low-voltage SRAM. IEEE design & test of computers, 2010, 28(1): 32-43.

[8] Park J W, Kim Y G, Kim I K, et al. Performance characteristics of SOI DRAM for low-power application. IEEE Journal of Solid-State Circuits, 1999, 34(11): 1446-1453.

[9] Godse R, McPadden A, Patel V, et al. Memory technology enabling the next artificial intelligence revolution. 2018 IEEE Nanotechnology Symposium (ANTS). IEEE, 2018: 1-4.

[10] Raj B, Suman A, Singh G. Analysis of power dissipation in DRAM cells design for nanoscale memories. International Journal of Information Technology and Knowledge Management, 2009, 2(2): 371-374.

[11] Mandelman J A, Dennard R H, Bronner G B, et al. Challenges and future directions for the scaling of dynamic random-access memory (DRAM). IBM Journal of Research and Development, 2002, 46(2.3): 187-212.

[12] Zhenyu C. Research and Application of DRAM Electrical Stress Aging Testing. Shandong University, 2023.